時間:2017-06-29 來源:互聯網 瀏覽量:

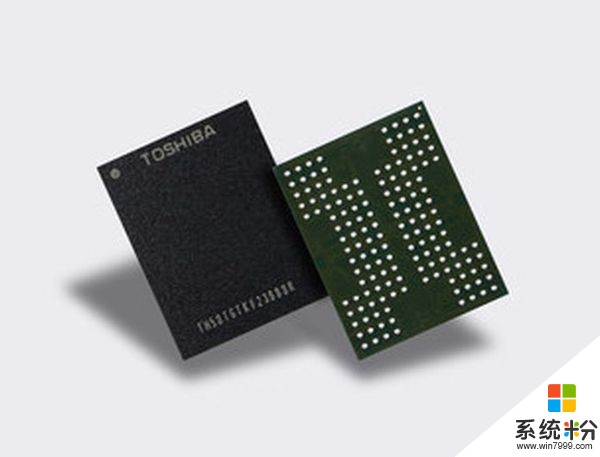

東芝今日宣布其成功開發出了全球首款 4-bit 3D 閃存(QLC),有望帶來更低的製造成本和更高的存儲密度。 閃存通過一串帶有電荷的浮動門晶體管來存儲數據(賦予“0”或“1”即 1-bit),這些存儲塊可以二維(平麵型 NAND)或三維(3D NAND)堆疊的形式排列,然後用更多電荷值來對應存儲更多位元的信息。比如四級(2-bit)閃存被稱為 MLC、八級(3-bit)則為稱為 TLC 。

QLC 進一步提升到了 16 級(4-bit),可將每格劃分出 16 個單元,從而實現更大的存儲容量。曾幾何時,業界難以突破 TLC 所需區分的精確電荷。但最新的進展是,東芝已開發出了 64 層堆疊的 QLC 3D NAND 。

該方法將核心存儲容量提升到了 768 gigabit,較 TLC 的 512 gigabit 有了顯著提升。東芝表示,新 QLC 核心能夠 16 片堆疊,從而實現 1.5TB 的存儲容量。

據悉,東芝已於本月早些時候開始向製造商出貨 3D QLC NAND 樣片,以供其評估。至於其何時走向消費級市場,目前暫不得而知。