時間:2020-02-04 來源:互聯網 瀏覽量:

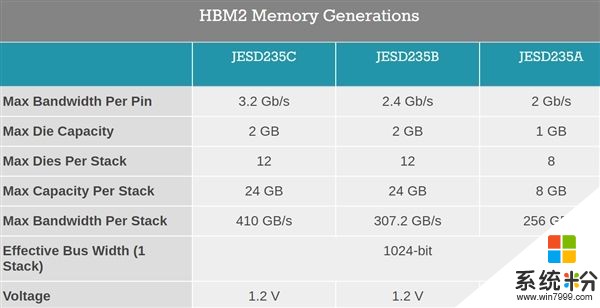

本周,固態存儲協會(JEDEC)發布第三版HBM2存儲標準JESD235C, 將針腳帶寬提高到3.2Gbps,前兩版中依次是2Gbps、2.4Gbps,環比提升33% 。

按照設計規範,單Die最大2GB、單堆棧12 Die(無標準高度限製),也就是24GB容量,匹配1024bit位寬,單堆棧理論最大帶寬410GB/s。對於支持四堆棧(4096bit)的圖形芯片來說,總帶寬高達1.64TB/s。

第三代HBM2的電壓和上一版一致,為1.2V,比第一代的1.35V有所下降。

簡單比較下,常見高端獨顯采用的256bit GDDR6,按照14Gbps的針腳帶寬計算,總帶寬448GB/s,也就是第三代HBM2一個堆棧的水平。考慮到HBM2更容易擴充總線寬度,GDDR6過猶不及, 況且單堆棧最大容量就能達到24GB,四堆棧直逼100GB。

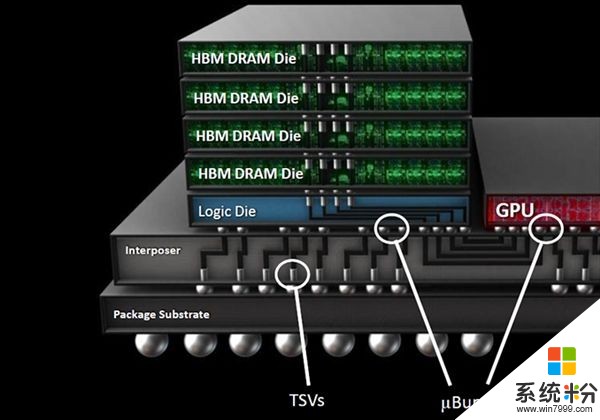

圖為HBM顯存示意

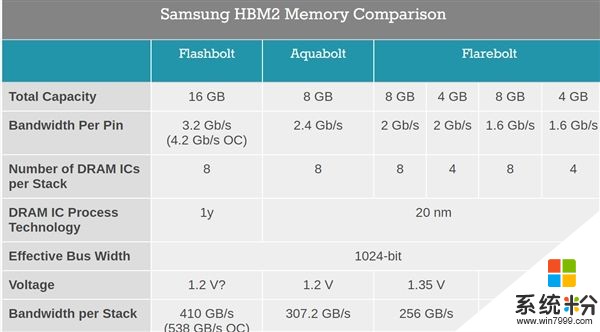

事實上,3.2Gbps的第三代HBM2早先已經由三星和SK海力士提出,並更名為HBM2E,這種說法也得到了JEDEC默認。

在JESD235C標準發布的同時,三星宣布,名為Flashbolt(前兩代名為Flarebolt和Aquabolt)的第三代HBM2(HBM2E)存儲芯片將在上半年量產,單顆最大容量16GB,由16Gb的單Die通過8層堆疊而成。

三星的第三代HBM2E甚至支持超頻,單針腳可加速到4.2Gbps,單堆棧最大帶寬從而升至538GB/s。

【作者:萬南】